ULX3S JTAG Connection with ft232r

Note: this page is for connecting a secondary JTAG connection to the Libre-SOC Core, in order to test the actual HDL implementation of JTAG. "Normal" JTAG documentation instructs you how to connect to the FPGA hard-macro JTAG port (in some fashion). Whilst the FPGA has a JTAG port as a hard-macro these instructions do not apply to that: they apply specifically to actual implementation in HDL of a JTAG TAP interface suitable for deployment on an ASIC, and, consequently, in order to test that, four GPIO pads had to be picked to bring those signals out. These instructions describe how to correctly wire up an FT232r to connect to those four GPIO pads.

Cross referenced with:

https://bugs.libre-soc.org/show_bug.cgi?id=517

http://lists.libre-soc.org/pipermail/libre-soc-dev/2020-October/000873.html

https://www.amazon.co.uk/Elegoo-120pcs-Multicolored-Breadboard-arduino-colorful/dp/B01EV70C78/

Original Instructions

See https://bugs.libre-soc.org/show_bug.cgi?id=517#c0

Checklist based on above

For god's sake make sure you get this right, TRIPLE check everything.

DO make sure to only drive an input as an input, and to only drive an output as an output.

DO make sure to only wire up 3.3V to 3.3V and to only wire up GND to GND with the jumper-cables.

DO make sure that before even thinking of uploading to and powering up the FPGA that everything has been THOROUGHLY triple-checked.

If you violate any of the above stated hard-and-fast rules you will end up learning the hard way by DESTROYING the FPGA.

To start we have to ensure we have a safe set up.

| Checklist Step |

|---|

| Ensure power is disconnected from FPGA |

| Ensure ft232r USB is disconnected |

| Ensure FPGA USB is disconnected |

Now lets review all of the relevant material on this page before we begin the wiring process.

| Checklist Step |

|---|

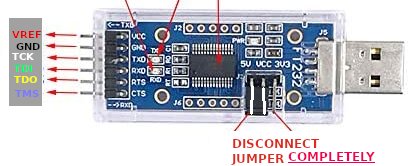

| Review the ft232r Connector diagram and table |

| Review the connections table for your model of fpga |

| Ensure the orientation of the FPGA and ft232r match that of the images and diagrams on this page |

Next we will wire up the ft232r and our FPGA in three separate stages.

First we will attach one end of a MALE-TO-MALE (MTM) jumper cable to each necessary female header pin-hole on the ft232f.

Then we will attach one end of a FEMALE-TO-FEMALE (FTF) cable to each male header pin on the FPGA.

Finally, we will connect the wires from the ft232r to the wires from the FPGA by matching the colours of the wires.

This way you do not lose the connections when you want to disconnect and store the two devices. We are using FEMALE-TO-FEMALE jumper cables on the male header pins of the FPGA so that the wires do not randomly damage the bare PCB due to a short.

We will wire each of the pins on the the ft232r according to the diagrams, tables, and images on this page.

| Action | Colour | Pin Name |

|---|---|---|

| Attach MTM | Black | GND |

| Attach MTM | Brown | TMS |

| Attach MTM | Red | VCC |

| Attach MTM | Orange | TCK |

| Attach MTM | Yellow | TDI |

| Attach MTM | Green | TDO |

Next, we will wire each of the pins on the the FPGA according to the diagrams, tables, and images on this page.

Follow this section if you have the ULX3S FPGA:

| Action | Colour | Pin # | Pin Name |

|---|---|---|---|

| Attach FTF | Red | 2 | VREF |

| Attach FTF | Black | 4 | GND |

| Attach FTF | Yellow | 5 | TDI |

| Attach FTF | Brown | 6 | TMS |

| Attach FTF | Orange | 7 | TCK |

| Attach FTF | Green | 8 | TDO |

Follow this section if you have the Versa ECP5 FPGA:

| Action | Colour | X3 Pin # | Pin Name |

|---|---|---|---|

| Attach FTF | Red | 39 | VREF |

| Attach FTF | Black | 1 | GND |

| Attach FTF | Yellow | 4 | TDI |

| Attach FTF | Brown | 5 | TMS |

| Attach FTF | Orange | 6 | TCK |

| Attach FTF | Green | 7 | TDO |

Final steps for both FPGA boards:

| Checklist Step |

|---|

| Check each jumper wire connection between the corresponding pins on the FPGA and the ft232r THREE times |

| lckl check for ground loops? |

Finally, we will connect the jumper cables of the same colour from ft232r and the FPGA.

| Checklist Step |

|---|

| Attach the ends of the RED jumper cables |

| Attach the ends of the BLACK jumper cables |

| Attach the ends of the YELLOW jumper cables |

| Attach the ends of the BROWN jumper cables |

| Attach the ends of the ORANGE jumper cables |

| Attach the ends of the GREEN jumper cables |

lckl if both the micro-usb cable and the ft232r GND and VCC wires are connected to the fpga will this result in volatage fighting where the fpga will be damaged?

Finally, plug in the USB end of the USB-to-MicroUSB cable that is plugged into the ft232r into your computer. Begin testing the SOC on the FPGA (instructions to follow).

Connecting the dots:

Accurate render of board for reference https://github.com/emard/ulx3s/blob/master/pic/ulx3st.jpg

Litex platform file https://github.com/litex-hub/litex-boards/blob/master/litex_boards/platforms/ulx3s.py

("gpio", 0,

Subsignal"p", Pins("B11")),

Subsignal("n", Pins("C11")),

IOStandard("LVCMOS33")

),

("gpio", 1,

Subsignal("p", Pins("A10")),

Subsignal("n", Pins("A11")),

IOStandard("LVCMOS33")

),

ULX3S FPGA constraints file https://github.com/emard/ulx3s/blob/master/doc/constraints/ulx3s_v20.lpf#L341-342

LOCATE COMP "gp[0]" SITE "B11"; # J1_5+ GP0 PCLK

LOCATE COMP "gn[0]" SITE "C11"; # J1_5- GN0 PCLK

LOCATE COMP "gp[1]" SITE "A10"; # J1_7+ GP1 PCLK

LOCATE COMP "gn[1]" SITE "A11"; # J1_7- GN1 PCLK

ULX3S FPGA Schematic https://github.com/emard/ulx3s/blob/master/doc/schematics_v308.pdf

J1 J2 PIN number 1-40 is for FEMALE 90° ANGLED header.

For MALE VERTICAL header, SWAP EVEN and ODD pin numbers.

J1

Label [GP{x}]|PCB pin label|[GN{x}] Label

(Pin count +)(Pin count -)

_________________V__________V________________

IO VOLT REF 3V3 2 |3.3V| 1 NOT CONNECTED

[GND] 4 | -| | 3 NOT CONNECTED

PCLKT0_0 [GP0] 6 | 0 | 5 [GN0] PCLKC0_0

PCLKT0_1 [GP1] 8 | 1 | 7 [GN1] PCLKC0_1

GP,GN 0-7 single-ended connected to Bank0

GP,GN 8-13 differential bidirectional connected to BANK7

Connecting all the dots:

Board pin # (count) | Board pin label # | FPGA IO PAD | GPIO # (n/p) | Label |

5 (J1_5-) | 0 | C11 | gn[0] | PCLKC0_0 |

6 (J1_5+) | 0 | B11 | gp[0] | PCLKT0_0 |

7 (J1_7-) | 1 | A11 | gn[1] | PCLKC0_1 |

8 (J1_7+) | 1 | A10 | gp[1] | PCLKT0_1 |

As noted in the schematic pins GP,GN 0-7 are single ended non-differential pairs, whereas pins GP,GN 8-13 I haven't mapped out here as they are bidirectional differential pairs.

List of connections (default physical pin numbers for FT232R in 28-pin SSOP package):

- RXD(5) - TDI

- TXD(1) - TCK

- RTS(3) - TDO

- CTS(11) - TMS

- DTR(2) - TRST

- DCD(10) - SRST

/**

* FT232R GPIO bit number to RS232 name

*/

#define FT232R_BIT_COUNT 8

static char *ft232r_bit_name_array[FT232R_BIT_COUNT] = {

"TXD", /* 0: pin 1 TCK output */

"RXD", /* 1: pin 5 TDI output */

"RTS", /* 2: pin 3 TDO input */

"CTS", /* 3: pin 11 TMS output */

"DTR", /* 4: pin 2 /TRST output */

"DSR", /* 5: pin 9 unused */

"DCD", /* 6: pin 10 /SYSRST output */

"RI" /* 7: pin 6 unused */

};

static int tck_gpio; /* initialized to 0 by default */

static int tdi_gpio = 1;

static int tdo_gpio = 2;

static int tms_gpio = 3;

static int ntrst_gpio = 4;

static int nsysrst_gpio = 6;

ft232 pin and wire colour table converted to jtag signal names:

|-------|------|--------|----------| | Pin # | JTAG | FT232 | Colour | |-------|------|--------|----------| | 1 | VCC | VCC | Red | | 2 | GND | GND | Black | | 3 | TCK | TXD | White | | 4 | TDI | RXD | Green | | 5 | TDO | RTS | Yellow | | 6 | TMS | CTS | Blue | |-------|------|--------|----------| ``` Proposed FPGA External Pin to ft232r JTAG pin connections:

all pin #'s have headers pins on the fpga unless denoted as (no header)

______________________________________________________________________________

| | board | | | | |

| | label | | | ft232r JTAG | |

| pin # | # | FPGA IO PAD |GPIO # (n/p) | Pin # (Signal)|Wire Colour|

|_____________|_______|_____________|_____________|________________|___________|

|1 (no header)| 3.3v |NOT CONNECTED|NOT CONNECTED| NOT CONNECTED | NOT |

|2 | 3.3v | IO VOLT REF | IO VOLT REF | 3 (VCC) | Red |

|3 (no header)|-|(GND)|NOT CONNECTED|NOT CONNECTED| NOT CONNECTED | NOT |

|4 |-|(GND)| NONE | GND | 1 (GND) | Black |

|5 (J1_5-) | 0 | C11 | gn[0] | 5 (TDI) | Green |

|6 (J1_5+) | 0 | B11 | gp[0] | 2 (TMS) | Blue |

|7 (J1_7-) | 1 | A11 | gn[1] | 4 (TCK) | White |

|8 (J1_7+) | 1 | A10 | gp[1] | 6 (TDO) | Yellow |

|_____________|_______|_____________|_____________|________________|___________|

Complete diagram:

Pins intentionally have no header or are not connected to the ft232 are marked

and therefore have no value are marked with 'NOT'

(ft232r# JTAG) = (ft232r pin # JTAG signal name)

J1

Wire Wire

Colour [GP{x}]|PCB label|[GN{x}] Colour

(ft232r# JTAG) (Pin count +)(Pin count -) (ft232r# JTAG)

______________________V__________V_______________________

| |

|(3 VCC) red [VREF] 2 |3.3V| 1 NOT NOT NOT |

|(1 GND) black [GND] 4 | -| | 3 NOT NOT NOT |

|(2 TMS) Blue [GP0] 6 | 0 | 5 [GN0] Green (5 TDI) |

|(6 TDO) Yellow [GP1] 8 | 1 | 7 [GN1] White (4 TCK) |

|_________________________________________________________|

Images of wires on ulx3s FPGA and on ft232r (lkcl to update images for Versa ECP5)

Image of JTAG jumper wire connections on ULX3S FPGA side:

Image of JTAG jumper wire connections on ft232r side:

Colour markings on ft232r side:

VERSA ECP5 Connections

Table of connections:

| X3 pin # | FPGA IO PAD | Function | FT232 | Wire Colour |

|---|---|---|---|---|

| 39 +3.3V | 3.3V supply | (VCC) | VREF | Red |

| 1 GND | GND | (GND) | GND | Black |

| 4 IO29 | B19 | (TDI) | RXD | Green |

| 5 IO30 | B12 | (TMS) | CTS | Blue |

| 6 IO31 | B9 | (TCK) | TXD | White |

| 7 IO32 | E6 | (TDO) | RTS | Yellow |